Its main feature is the user-customizable instruction set. Low power, configurable and extensible processor Tensilica’s Xtensa.

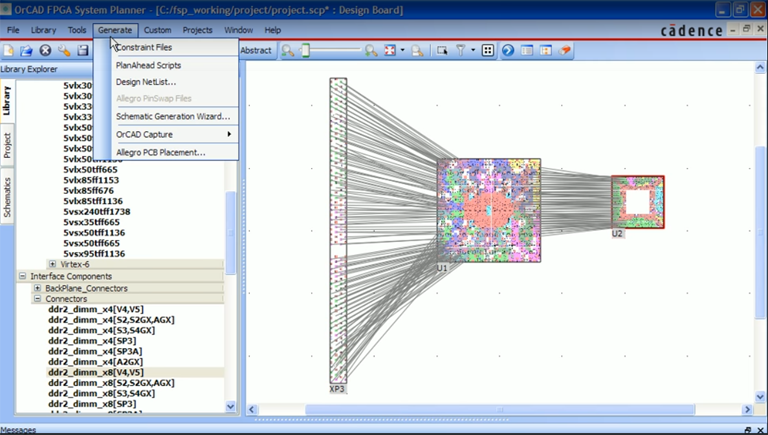

CADENCE FPGA SIMULATION SOFTWARE

Simulation accelerator tool IMAGE from Powai labs to enable hardware acceleration of HDL code.įPGA kits and programming software from Xilinx and Altera.

PCB design tools from Cadence and Mentor Graphics for designing of circuit boards for IC testing and development. These same test benches can be used with FPGA and SoC development boards to verify HDL implementations in hardware. You can verify RTL against test benches running in MATLAB ® or Simulink ® using cosimulation with an HDL simulator. In the last 10 years, Cadence made emulation very easy-to-use with bring-up and turnaround times reaching simulation environment bring-up (and in some cases, becoming even better). TLM simulation and half on an FPGA board (much less costly than an emulator).

CADENCE FPGA SIMULATION FULL

Synthesis tools from Synplicity in addition to tools from earlier vendors. HDL Verifier lets you test and verify Verilog ® and VHDL ® designs for FPGAs, ASICs, and SoCs. The FPGA prototyping being used mostly for SW development while emulation is being used for HW/SW verification and full system validation. Towards end of 2002, we successfully beta-tested Cadence mixed-language.

Verilog and VHDL tools from Cadence, Synopsys, Mentor Graphics, Xilinx to write HDL code for digital circuits. System verliog tools from Bluspec and Coware to implement large gate count, IP based and bus intensive chips. We have EDA tools for design, simulation and verification (functional, timing, physical) for analog, digital, custom, mixed signal and RF IC domains from Cadence, Synopsys and Mentor Graphics.īackend tools from magma, Cadence, Synopsys for placement, routing, layout and layout verification and export to GDSII format.

0 kommentar(er)

0 kommentar(er)